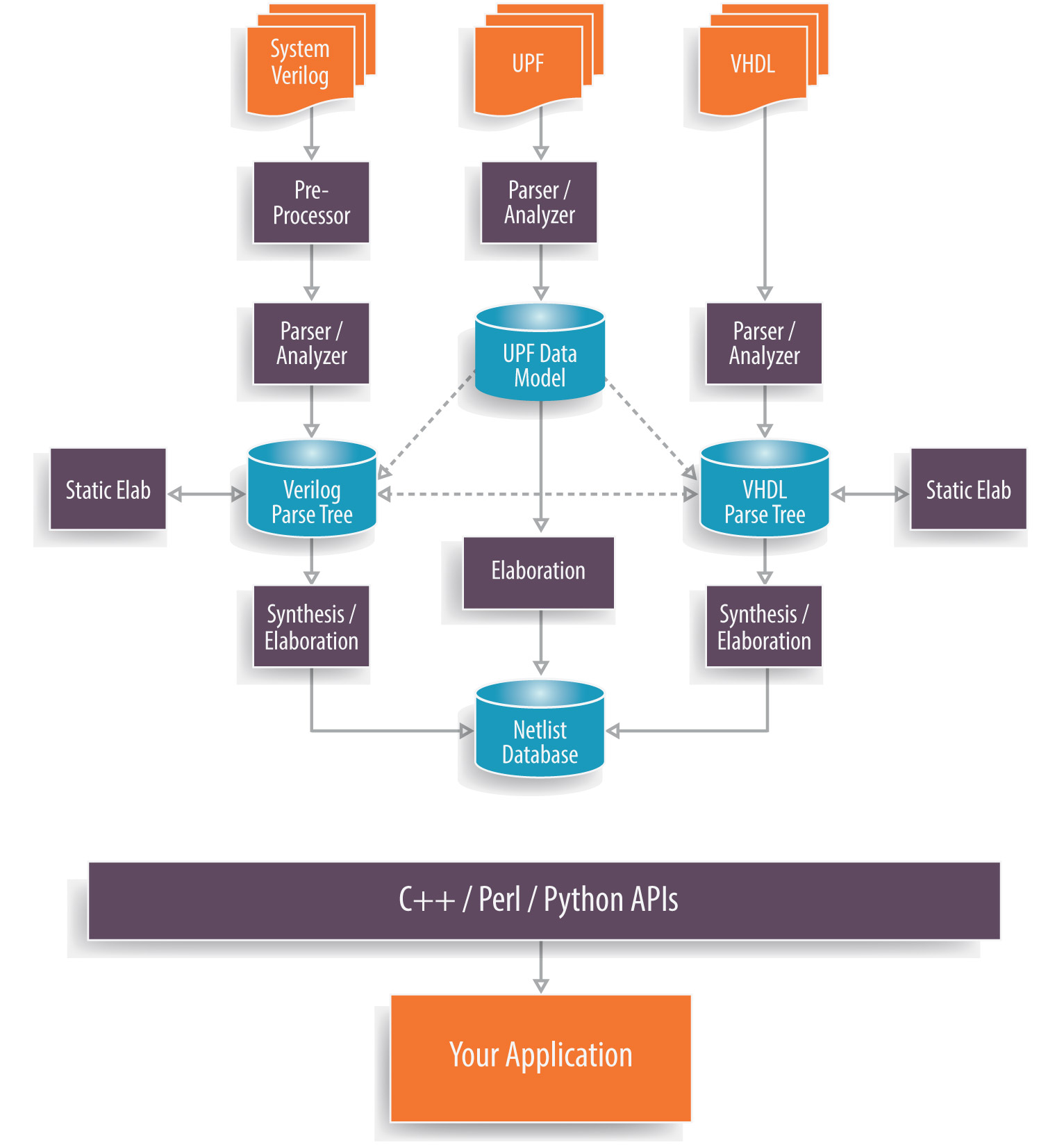

SystemVerilog (which includes Verilog 2001), VHDL, and UPF are parsed and processed in two steps, analysis and elaboration. Mixed VHDL and SystemVerilog compilation is fully supported.

Analysis creates parse-trees and performs type-inferencing to resolve the meaning of identifiers. The Parser/Analyzer modules support the entire SystemVerilog IEEE 1800 (including Verilog IEEE 1364), VHDL IEEE 1076, and UPF IEEE 1801 languages, all revisions, without any restrictions. The resulting parse trees / data models come with extensive APIs.

Elaboration supports both static elaboration and RTL elaboration. Static elaboration elaborates the entire language, and specifically binds instances to modules, resolves library references, propagates defparams, unrolls generate statements, and checks all hierarchical names and function/task calls. The result after static elaboration is an elaborated parse tree, appropriate for simulation like applications. RTL elaboration is limited to the synthesizable subset of the language. In addition to the static elaboration tasks for this subset, it generates sequential networks through flipflop and latch detection, and Boolean extraction. The result after RTL elaboration is a netlist, appropriate for applications such as logic synthesis and formal verification.

The netlist database stores RTL and netlist designs in a language-independent simple model based on generic gates such as DFF, AND, OR, MUX , etc.. The netlist database is common to both VHDL and SystemVerilog and has an efficient and clean API for easy integration into any existing database or object model.

- Very memory efficient. Average overall memory usage just 300 bytes/gate.

- Full hierarchy support, with grouping/ungrouping, etc.

- Support for buses.

- Compact storage of file/line/column origination info from RTL parsers.

- Simple and clean data model and procedural Interface for easy integration with your existing database.

SystemVerilog – VHDL – UPF –Verilog – AMS – netlist only – EDIF/SDF/LIberty – test suites

Do you want more information?

Try our Free 30-day Evaluation Package, our downloads page or just contact us.