Verific’s UPF parser supports the entire IEEE 1801 standard (UPF 1.0, 2.0, 2.1, 3.0) and creates a UPF data model.

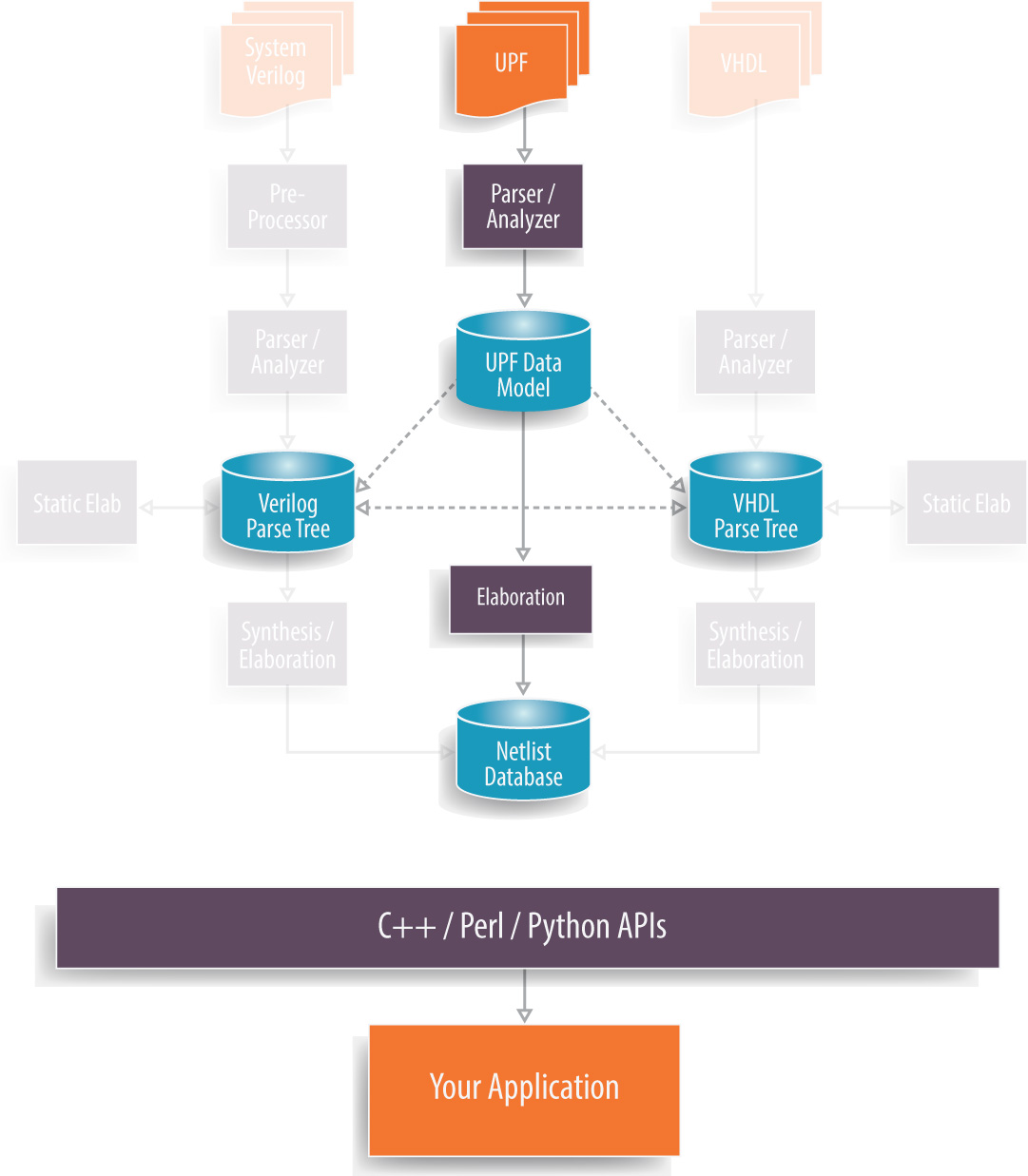

The UPF Parser is an integral component of Verific’s Parser Platform and interacts seamlessly with Verific’s standard SystemVerilog, VHDL, and Liberty parsers. It natively interfaces with Verific’s data structures, and also has the ability to interface with external (non-Verific) design data. The UPF Parser/Analyzer performs syntax and semantic checking, resolving a UPF specification into a power intent model that can be traversed and queried. Complete file / line / column information on UPF descriptions is maintained and Verific’s comprehensive error handler is included.

The UPF Elaborator applies the power intent model to the original HDL design. The result is a power-aware netlist with new instantiations of power-related cells, as well as any required supply network and corresponding control path logic. UPF concepts elaborated in an HDL design include logic and supply ports and nets, power switches,and retention, isolation, level-shifter and repeater cells.

Verific’s UPF parser is also easily integrated with external (non-Verific) data structures.

Do you want more information?

Try our Free 30-day Evaluation Package, our downloads page or just contact us.